- 全部

- 默认排序

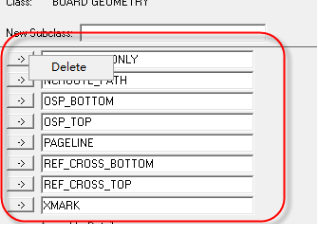

答:我们在进行PCB设计的时候,导入DXF文件后者其它参照的对象,都会在PCB中新建一些subclas层,累计的多了,subclass层就会非常多,所以我们这里讲解一下,如何去删除自己新建的subclass层,具体操作如下所示:

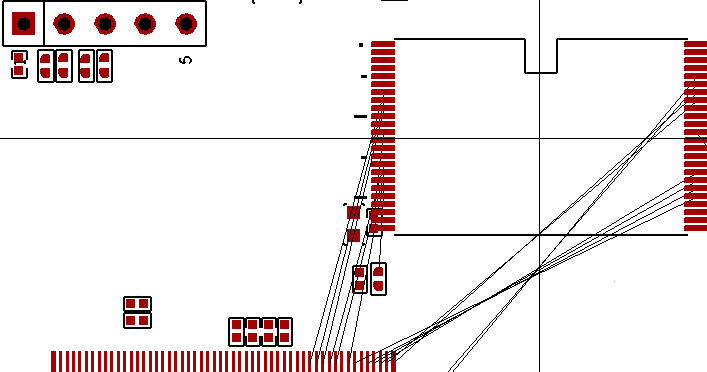

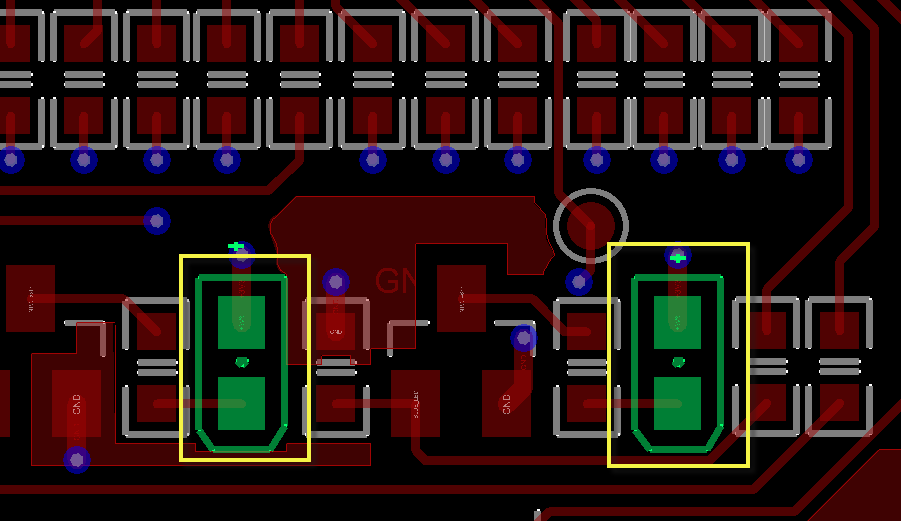

答:我们在进行布局的时候,执行移动命令,移动的时候会显示器件的飞线,方便引导工程师进行布局,如图6-213所示,移动哪个器件,哪个器件就会显示飞线。

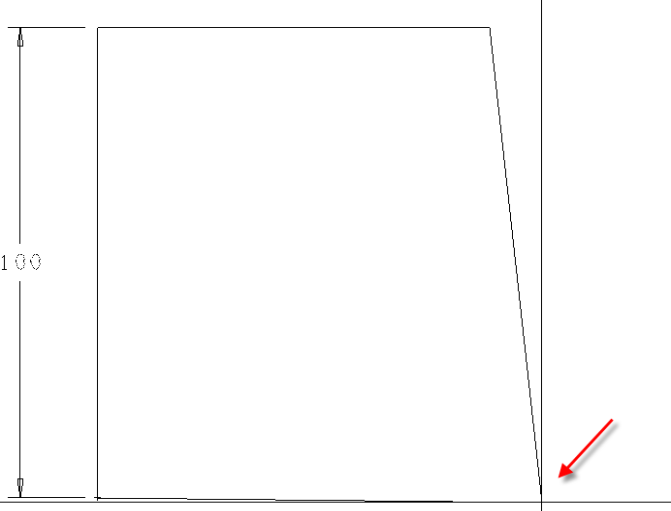

答:我们在进行PCB设计之前,都需要先绘制板框,在PCB绘制板框,都是绘制标准的,比如矩形、圆形,如果板框是异形的,一般是通过autocad软件绘制好之后,导入到PCB中。板框进行修改呢,也是如此,我们这里举例讲解一下,对于规则的板框绘制完成以后,我们应该如何对其进行修改,具体如下。

答:第一步,点击Display-Assign Color选项,如图6-218所示;

答:第一步,点击Shape-Select Shape or Void/Cavity选项,如图6-222所示;

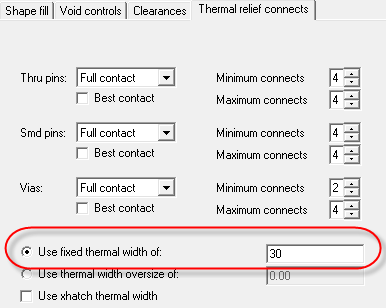

答:在做PCB设计过程中,叠层时可以选择是负片工艺还是正片工艺,如果层数较少,一般都可以正片处理,层数较多、数据量较大时会选择负片工艺对电源层进行处理。

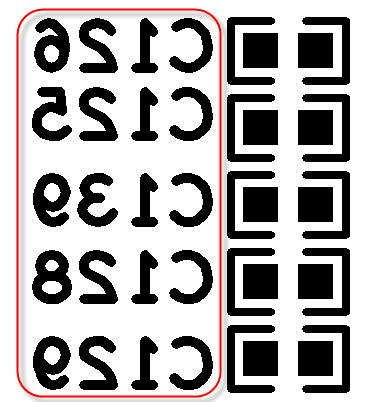

答:Allegro软件对于BOTTOM层的器件,其位号字符一般是镜像显示的,如图6-225示:

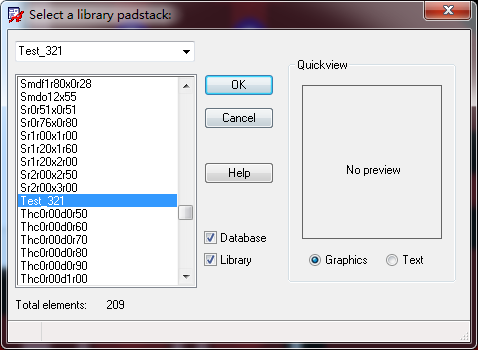

答:ICT (In Circuit Tester,自动在线测试仪)是印制电路板生产中重要的测试设备:用于焊接后快速测试元器件的焊接质量,能迅速定位焊接不良的引脚,以便及时进行补焊。体现在PCB设计上,则需要在设计中添加用于ICT测试的焊盘,并对符合测试点要求的焊盘添加测试点属性。因测试点焊盘和间距及位置有严格的要求,对于有ICT设计要求的板卡,建议在设计前就明确添加ICT的网络,拟定ICT的添加计划,在设计的过程中边布线边添加。如果在设计完后再添加ICT测试点,必将大量返工,甚至有的网络根本无法

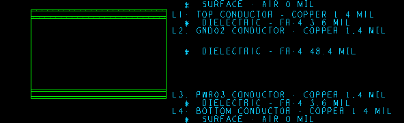

答:在生成的Gerber中,除了要将PCB上的走线、过孔等内容包含进去,还需要将PCB的叠层等信息制作进去,以便提供详细的文件给工厂生产,Allegro提供了一个直接提取设计参数生成的叠层表格的功能,减少了设计者的工作量。

扫码关注

扫码关注